2. 成都信息工程大学 控制工程学院,四川 成都 610054

2. School of Control Eng.,Chengdu Univ. of Info. Technol.,Chengdu 610054,China

目前,针对计算机节能的措施主要有两类:第1类主要考虑平台、中心、硬件的节能,并设计绿色平台架构,搭建节能中心,开发低功耗设备实现节能;第2类主要考虑软件的节能,从操作系统到应用软件寻找有效的节能措施。针对CPU节能,有较大影响的技术为动态电压频率调节技术、动态电源管理技术、温度管理技术等。其中,DVFS是应用最广泛的处理器节能技术,如何从处理器体系结构层面出发考虑优化DVFS策略为处理器节能提供了一种新的思路值得研究和探讨。

DVFS技术实现CPU节能的一些方法已经被提出,相关工作可以分为:

第1类依赖于任务执行的松弛时间。文献[1]首次将动态电压与频率调节技术用于处理器功耗优化,模拟任务执行的轨迹与松弛时间,在操作系统进行任务调度时,为每个任务设置一个新的运行频率;文献[2]提出通过CPU空闲时间与繁忙时间的比值自动设置处理器频率,被称为PAST算法,该算法利用空闲时间的大小作为寻找最优频率的标志;文献[3]提出一种依赖于任务时间间隔的频率调节算法,通过在不影响用户体验的情况下延长一定的任务执行时间来降低芯片功耗。这些策略需要预先知道任务的到达时间和执行时间。

第2类利用应用程序辅助指导DVFS进行频率调节。文献[4]提出一种基于应用程序前一段时间的工作信息对处理器进行动态调频的方法;文献[5]提出采用过去

第3类利用任务运行时特征来指导DVFS进行频率调节实现节能。文献[7]提出一种基于软件特征量优化DVFS的GPU节能模型;文献[8]针对单核处理器从系统组件对DVFS进行优化设计;文献[9]根据程序运行时访存阻塞的分布、计算负载等信息提出了一种在线的DVFS方法,该方法考虑了程序阶段行为和存储器停滞时间的运行时分布以及工作量;文献[10]提出一种依据最大和最小频率的线性结合方法来得到系统最优频率的方法,称为MMF-DVFS算法;文献[11]提出一种利用程序运行时的IPC (instructions per cycle)和处理器的频率之间的关系指导DVFS的方法降低能耗;文献[12]依据内存频率与阈值的关系优化DVFS;文献[13]根据MPI(last level cache misses per instruction)在程序中的分布、相应的能源消耗和其他统计信息将DVFS规划成MCKP(multiple choice knapsack problem)问题。虽然程序运行特征指导DVFS可以达到节能的目的,但是这些策略考虑特征数量不足,其他与处理器运行相关性较大特征没有被包含。

从体系结构层面出发提取相关特征量指导DVFS调频的研究较少,已有研究也多采用线性方法。本文深入分析处理器运行时特征从而提出BP-DVFS调频策略,该策略利用FPU-CPU模型对处理器下一时间段利用率的预测值进行处理器频率调节;FPU-CPU模型采用BP神经网络进行非线性拟合,预测的CPU利用率与实际值误差较小,使得BP-DVFS策略对处理器运行频率的调节更准确。

1 BP-DVFS策略与FPU-CPU模型本文所提出的BP-DVFS处理器调频策略基于所构建的FPU-CPU模型,模型假设处理器下一时间段利用率和处理器运行相关特征量存在非线性函数关系,采用BP神经网络进行非线性关系拟合;根据拟合得到的神经网络预测处理器下一时间段的利用率指导DVFS进行处理器调频。

本文主要研究处理器动态功耗部分。传统计算能耗的模型为:

| $E = P{\rm{ \times }}T = \int {P{\rm{d}}t} $ | (1) |

式中,

动态功率的计算模型为:

| ${P_{\rm d}} = C{\rm{ \times }}N{\rm{ \times }}{V^2}{\rm{ \times }}f$ | (2) |

式中,

| ${P_{\rm d}} = K{\rm{ \times }}{V^2}{\rm{ \times }}f$ | (3) |

由式(3)可知,由于

| ${P_{\rm d}} \approx {K'}{\rm{ \times }}{f^3}$ | (4) |

式中,

| ${W_{\rm d}} = \int_0^T {{K'}{\rm{ \times }}{f^3}{\rm d}t = {K'}{\rm{ \times }}{f^3}{\rm{ \times }}T = {C'}{\rm{ \times }}{f^2}} $ | (5) |

式中,

DVFS是处理器调频应用最广泛的技术,但因为其对处理器下一时间段运行情况考虑不足导致调频效果不佳。本文假设下一时间段CPU利用率与CPU运行中的某些事件特征量存在非线性关系,获得FPU-CPU模型如下:

| $l = f({C_1},{C_2},{C_3},{C_4},{C_5})$ | (6) |

式中:

因为实验所采集得到的数据数量级会有比较大的差别,例如,访存次数可能在3位数量级,而分支预测错误可能有7位数量级。因此,使用数据归一化把数据转化为[0,1]之间的数。所采用的数据归一化方法如下:

| $X_k' = ({X_k} - {X_{\min }})/({X_{\max }} - {X_{\min }})$ | (7) |

式中,

在BP神经网络根据输入指标得到输出后,还需要对该输出做相应的反归一化,反归一化公式为:

| $X = {X'}({X_{\max }} - {X_{\min }}) + {X_{\min }}$ | (8) |

式中,

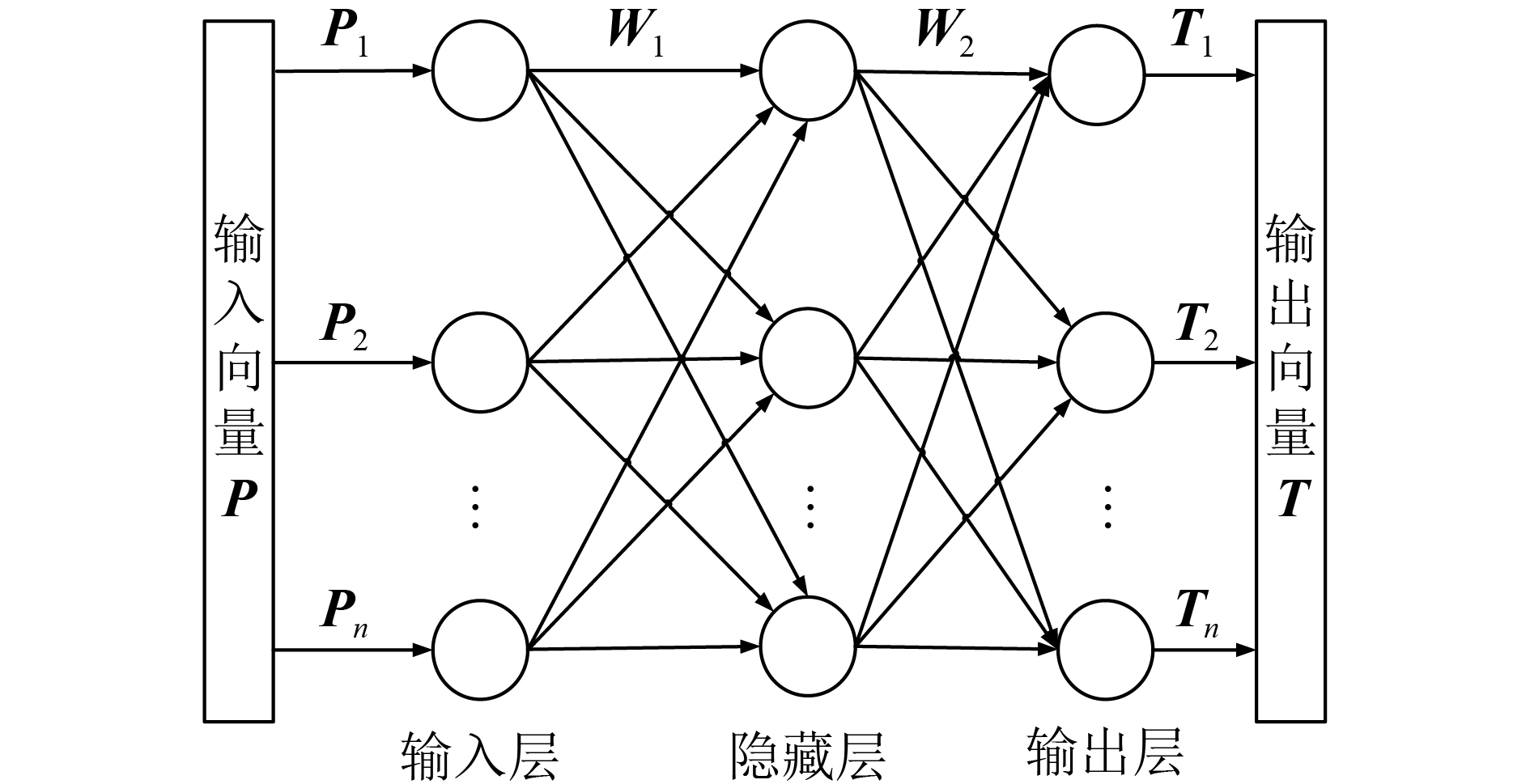

BP神经网络是目前应用最广泛的神经网络模型之一。神经网络有一个输入层、一个输出层、若干个隐藏层组成。BP神经网络的结构如图1[14]所示,其中,

|

| 图1 BP神经网络结构 Fig. 1 BP neural network structure |

1989年Hornik证明,只需一个包含足够多神经元的隐藏层,BP神经网络就能以任意精度逼近任意复杂度的连续函数。

根据上述BP神经网络的论述确定本文BP神经网络的结构如下:

1)隐藏层数的确定。Hecht-Nielson证明了对任何在闭区间内的连续函数,都可用单隐藏层的BP网络逼近,即一个3层的BP网络可完成任意的

2)节点数确定。输入层为

| ${n_1} = \sqrt {n + m} + a$ | (9) |

式中,

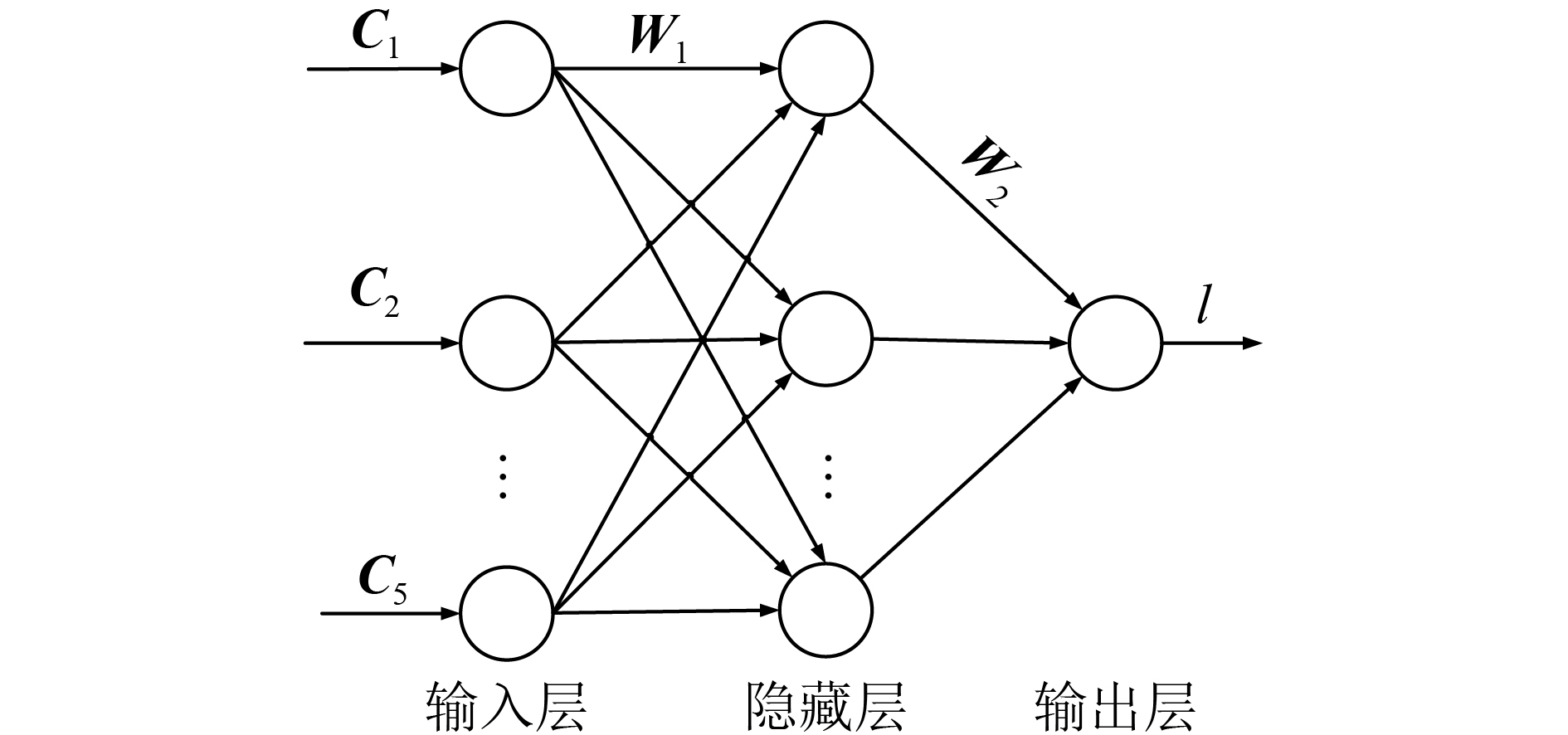

3)函数的确定。针对单隐藏层BP神经网络,输入层和隐藏层传递函数通常选用tansig函数,输出层传递函数一般采用purelin函数。通过多组实验发现,trainlm函数用在隐藏层,且节点数为11时,网络收敛速度和逼近误差达到令人满意的效果。因此,采用trainlm函数作为BP神经网络的训练函数,训练网络的隐藏层节点数确定为11。确定本文神经网络结构如图2所示。

|

| 图2 本文BP神经网络结构 Fig. 2 Proposed BP neural network structure |

输入变量

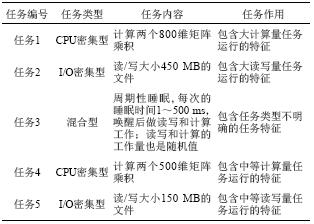

根据程序执行类型的不同,本文一共选择5个基准程序作为神经网络的训练集,分别是2个CPU密集型任务程序、2个I/O密集型任务程序、1个混合型任务程序。所选用程序具体情况如表1所示。

| 表1 基准程序介绍 Tab. 1 Introduction to benchmarking procedures |

|

通过对神经网络进行不断训练在误差MSE达到10–7情况下得到神经网络权值和阈值如下:

| $\begin{array}{l}{\mathit{\boldsymbol{W}}_1} = \left[\!\! \begin{array}{*{20}{c}} \;\;{- 0.416 \; 5 }&{ - 0.169 \; 6 }&{ - 1.450 \; 0 }&{ - 0.044 \; 2}& \;\;\;{ 0.456 \; 0}\\ \;\;\;\;\;{ 1.579 \; 4 }&{ - 1.116 \; 4 }&{ - 3.648 \; 6 }&{ - 0.165 \; 2 }& \;\;\;{ 3.164 \; 4}\\ \;\;{ - 9.831 \; 8 }& \;\;\;{ 1.444 \; 6 }& \;\;\;{ 1.793 \; 8 }& \;\;\;{ 1.235 \; 6 }&{ - 3.698 \; 9}\\ \;\;\;\;\;{ 2.358 \; 2 }& \;\;\;{ 2.266 \; 8 }& \;\;\;{1.466 \; 6 }& \;\;\;{1.591 \; 2 }& \;\;\;{ 1.012 \; 7}\\ \;\;{ - 5.784 \; 7 }& \;\;\;{ 3.014 \; 8 }& \;\;\;{ 1.142 \; 9 }&{- 1.810 \; 4 }&{ - 0.046 \; 1}\\ \;\;{ - 0.551 \; 4 }&{ - 2.200 \; 3}& \;\;\;{ 1.356 \; 0 }& \;\;\;{ 1.011 \; 7 }&{ - 1.231 \; 1}\\ \;\;\;\;\;{ 2.048 \; 3 }&{ - 0.682 \; 0 }& \;\;\;{ 2.954 \; 5 }& \;\;\;{1.549 \; 5 }&{- 0.676 \; 1}\\ \;\;\;\;\;{ 2.343 \; 4 }&{ - 1.352 \; 4 }& \;\;\;{ 2.179 \; 0 }&{- 1.578 \; 2 }&{ - 1.521 \; 6}\\ \;\;\;\;\;{ 5.069 \; 7 }&{ - 2.825 \; 1 }& \;\;\;{ 0.695 \; 0 }&{- 1.270 \; 8 }&{ - 2.510 \; 2}\\ { - 10.435 \; 6}& \;\;\;{ 3.649 \; 6 }&{ - 0.117 \; 5 }& \;\;\;{ 2.354 \; 1 }& \;\;\;{ 2.775 \; 3}\\ \;\;{ - 0.832 \; 9 }&{ - 0.385 \; 9}&{ - 3.593 \; 3}& \;\;\;{ 2.239 \; 2 }&{ - 0.645 \; 5}\end{array} \right],\;\;{\mathit{\boldsymbol{W}}_2} = \left[\!\! \begin{array}{l} - 1.504 \; 9\\ - 2.891 \; 7\\ - 2.069 \; 1\\ - 2.197 \; 6\\ - 0.186 \; 4\\ - 0.258 \; 4\\ - 0.463 \; 5\\ \;\;\;0.091 \; 6\\ - 5.847 \; 6\\ - 2.160 \; 7\\ \;\;\;0.050 \; 1\end{array}\!\! \right]\text{。}\end{array}$ | (10) |

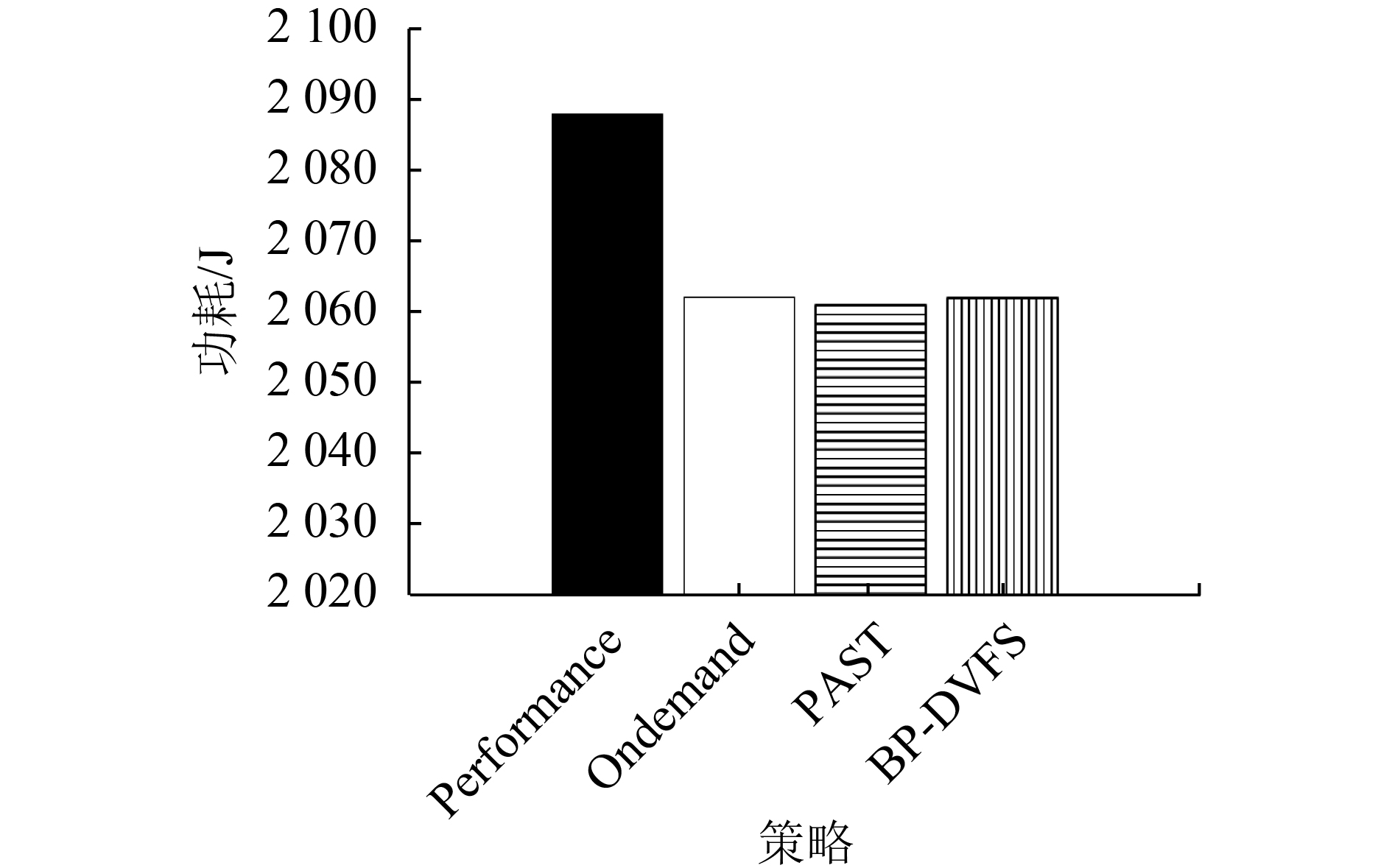

实验在3.13.0内核版本的Linux操作系统上运行,系统位数为32位;搭载Intel i3处理器,运行频率范围为1.2~2.4 GHz;RAM大小为4 GB。选用CPU密集型任务、I/O密集型任务、混合型任务3种程序,分别在Performance[16]、Ondemand[17]、PAST[2]、BP-DVFS 4种策略调频下运行。其中,Performance为Linux内核自带的节能策略,Ondemand为Linux内核默认的节能策略,PAST是前人研究的策略,BP-DVFS策略为本文采用FPU-CPU调频的策略。采用功耗测量仪KA3005P数控直流电源测得功耗值。系统在只运行4种策略而不运行任务程序的200 s内策略功耗如图3所示。

|

| 图3 策略功耗 Fig. 3 Power consumption of different strategies |

由图3可知,4种处理器调频策略中除Performance策略因为一直在高频率运行而功耗较大外,其他3种策略自身功耗相差不大。

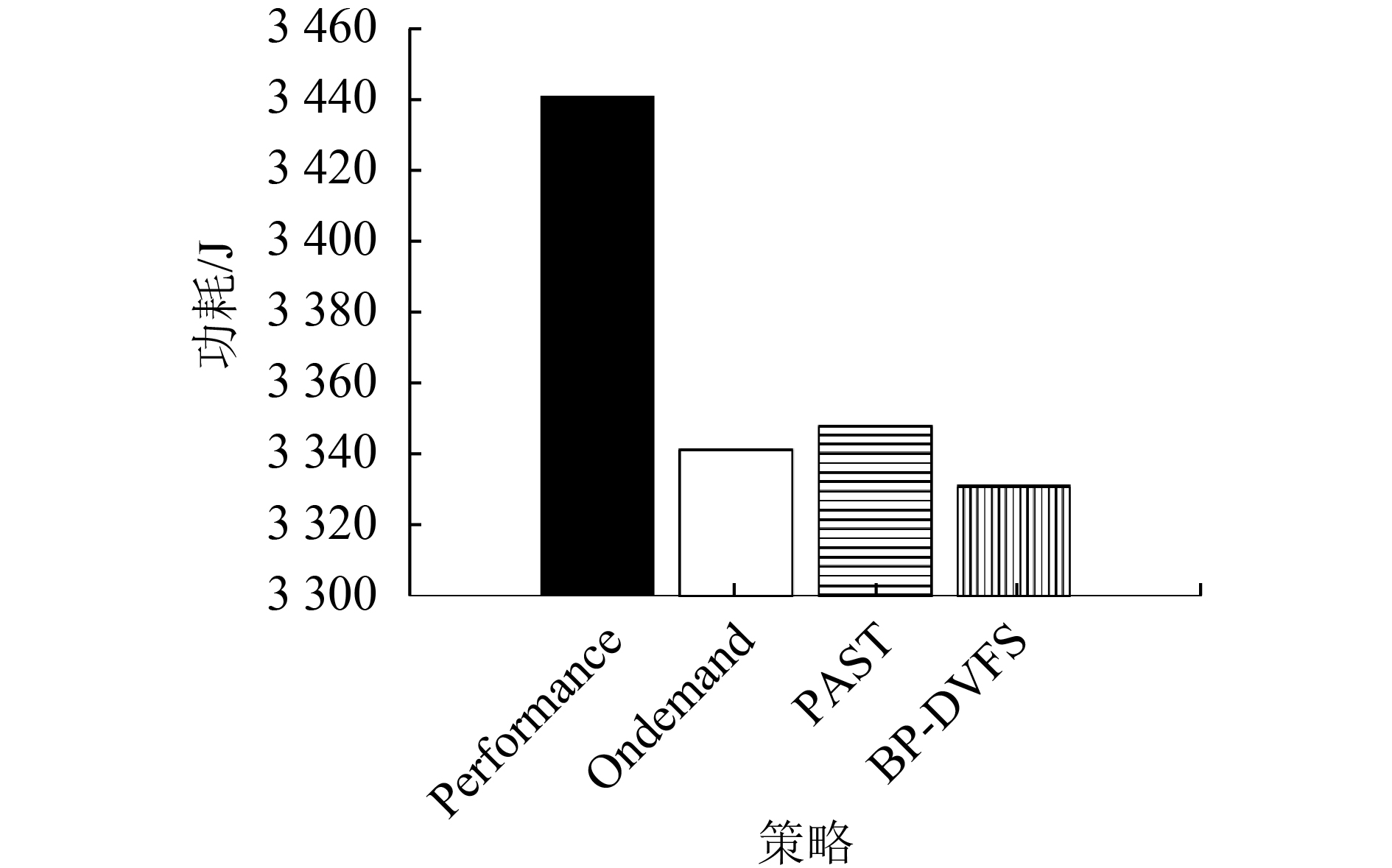

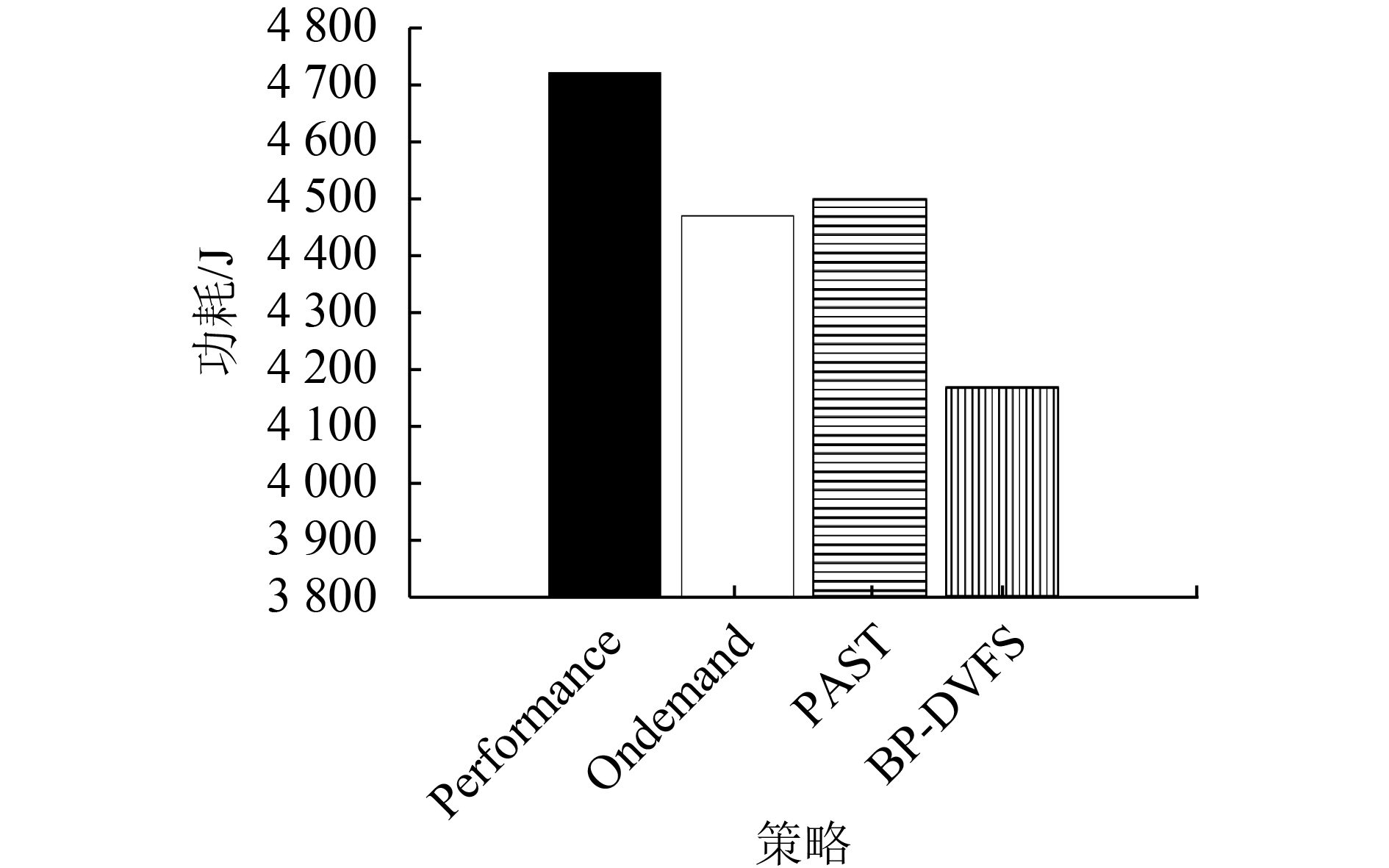

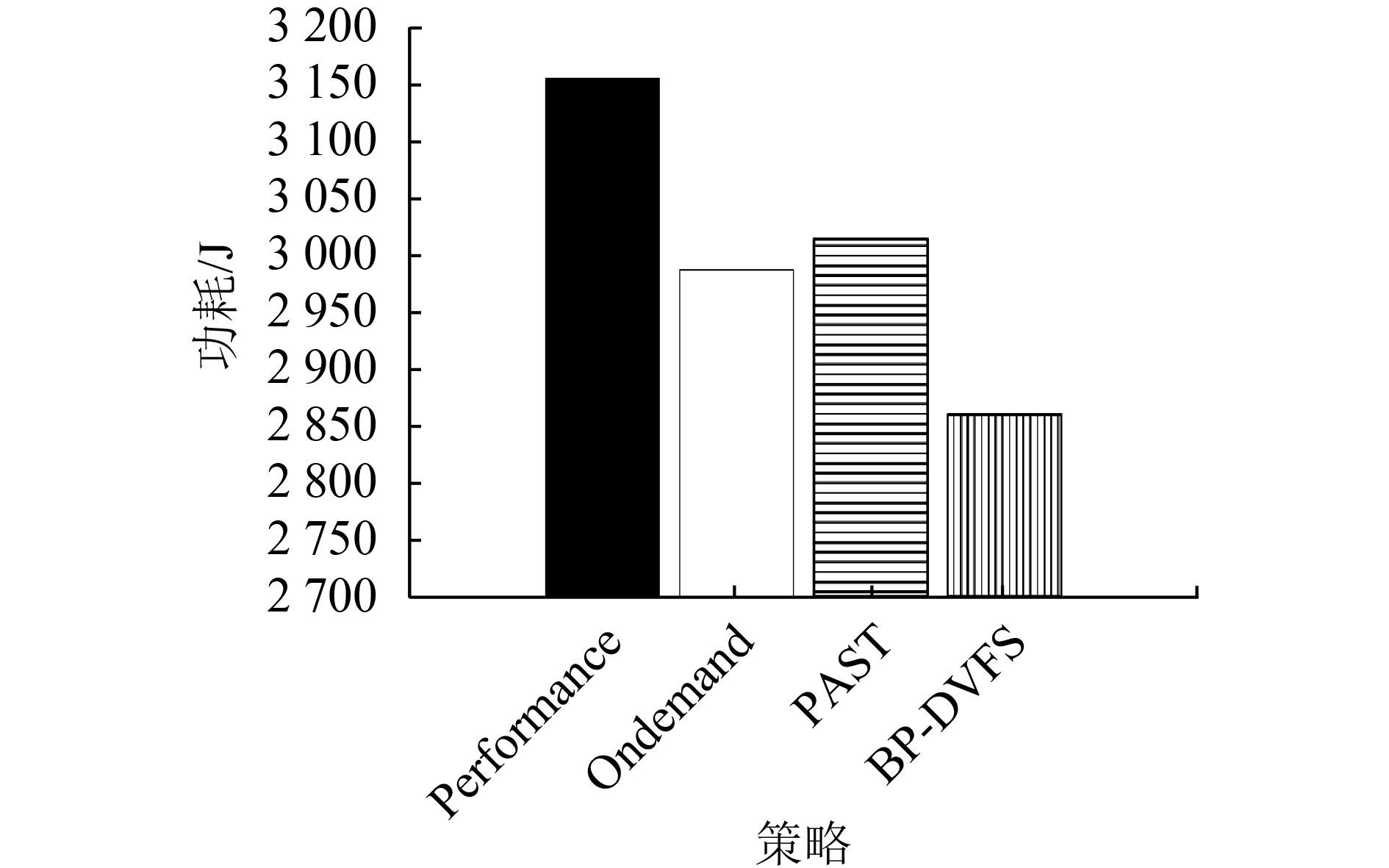

4种策略在本文选取的3种不同类型任务上的运行功耗情况,如图4~6所示。

|

| 图4 CPU密集型任务的功耗 Fig. 4 Power consumption of CPU-intensive task |

|

| 图5 I/O密集型任务的功耗 Fig. 5 Power consumption of I/O intensive tasks |

|

| 图6 混合型任务的功耗 Fig. 6 Power consumption of hybrid tasks |

由图4可知,针对CPU密集型任务程序,Performance策略功耗最大,其余3种策略效果差别不大,本文所采用的基于FPU-CPU调频方法的BP-DVFS策略的节能效果较好。由于CPU密集型任务对CPU资源的需求较高,CPU需要处于较高的运行频率,故4种策略都会将相应CPU的运行频率调到最高值;并且,实验中运行的CPU密集型任务是矩阵乘法运算,只在单核上运行,除Performance策略外,其他策略则会将其余CPU调节到运行频率。

对于I/O密集型任务,每个CPU核均衡运行任务。该任务要频繁访问内存,所以CPU频率抖动厉害,一般会在40%范围变动。观察图5可知:Performance策略一直处于高频运行故功耗大;Ondemand策略对CPU利用率预测不是很准确,故执行该策略的节能效果也不太理想。

由图6可知,BP-DVFS策略相比于其他策略效果明显。这主要是因为混合型任务CPU利用率抖动频繁,Ondemand和PAST对CPU下一阶段利用率预测出现失误,故其他策略不能有效对CPU运行频率进行调节。

综合观察图4、5、6可知:Performance策略在4种处理器调频中节能效果最差;Ondemand策略作为Linux默认CPU调频策略具有一定竞争力;BP-DVFS策略在3种类型任务上都有较好的效果,对3种任务程序都可实现CPU的低功耗运行。

通过实验证明了第2节假设下一时间段CPU利用率与CPU资源有关的事件存在非线性函数关系的合理性,进而验证了所提出的BP-DVFS策略和FPU-CPU模型的合理性及有效性。

4 结束语本文在研究传统的DVFS基础上,针对前人的研究未能考虑处理器下一阶段的利用率。假设下一时间段CPU利用率与CPU资源有关的事件存在非线性函数关系。提出一种BP-DVFS策略和基于FPU-CPU的CPU利用率预测模型,提取与处理器运行相关的5个相关事件指令执行、访存、硬件中断、上下文切换、分支预测错误,度量相关事件的值为IPC、访存次数、硬件中断次数、上下文切换次数、分支预测错误次数。采用BP神经网络进行拟合,提高了预测CPU利用率的准确度,优化了传统DVFS方法,降低了CPU运行能耗。

未来研究工作为:一是,对模型的拟合采用的是BP神经网络,虽然有效,但是该网络历史久远,随着技术的发展一定会有更好的方法;二是,对访存事件,可以考虑把访存次数分成访问高速缓存、访问内存等更微观情况。

| [1] |

Weiser M,Welch B,Demers A,et al.Scheduling for reduced CPU energy[C]//Proceedings of the 1st USENIX Conference on Operating Systems Design and Implementation.Berkeley:USENIX Association,1994:Article No. 2.

|

| [2] |

Pering T,Burd T,Brodersen R.Voltage scheduling in the IpARM microprocessor system[C]//Proceedings of the 2000 International Symposium on Low Power Electronics and Design.Rapallo:IEEE,2000:96-101.

|

| [3] |

Pering T,Burd T,Brodersen R.The simulation and evaluation of dynamic voltage scaling algorithms[C]//Proceedings of the 1998 International Symposium on Low Power Electronics and Design.Monterey:IEEE,1998:76-81.

|

| [4] |

Dhodapkar A S, Smith J E. Managing multi-configurable hardware via dynamic working set analysis[J]. ACM SIGARCH Computer Architecture News, 2002, 30(2): 233-244. DOI:10.1145/545214 |

| [5] |

Grunwald D,Morrey C B Ⅲ,Levis P,et al.Policies for dynamic clock scheduling[C]//Proceedings of the 4th Conference on Symposium on Operating System Design & Implementation.Berkeley:USENIX Association,2000:Article No. 6.

|

| [6] |

Govil K,Chan E,Wasserman H.Comparing algorithm for dynamic speed-setting of a low-power CPU[C]//Proceedings of the 1st Annual International Conference on Mobile Computing and Networking.New York:ACM,1995:13–25.

|

| [7] |

Li Junke, Guo Bing, Shen Yan. A modeling approach for energy saving based on GA-BP neural network[J]. Journal of Electrical Engineering & Technology, 2016, 11(5): 1289-1298. |

| [8] |

Choi K,Lee W,Soma R,et al.Dynamic voltage and frequency scaling under a precise energy model considering variable and fixed components of the system power dissipation[C]//Proceedings of the 2004 IEEE/ACM International Conference on Computer-Aided Design.San Jose:IEEE,2004:29-34.

|

| [9] |

Kim J, Yoo S, Kyung C M. Program phase-aware dynamic voltage scaling under variable computational workload and memory stall environment[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2011, 30(1): 110-123. DOI:10.1109/TCAD.2010.2068630 |

| [10] |

Rizvandi N B,Taheri J,Zomaya A Y,et al.Linear combinations of dvfs-enabled processor frequencies to modify the energy-aware scheduling algorithms[C]//Proceedings of the 10th IEEE/ACM International Conference on Cluster,Cloud and Grid Computing (CCGrid).Melbourne:IEEE,2010:388-397.

|

| [11] |

Kotla R,Ghiasi S,Keller T,et al.Scheduling processor voltage and frequency in server and cluster systems[C]//Proceedings of the 19th IEEE International Parallel and Distributed Processing Symposium.Denver:IEEE,2005:234.2.

|

| [12] |

Kim S G, Eom H S, Yeom H Y. Energy-centric DVFS controlling method for multi-core platforms[J]. Computing, 2014, 96(12): 1163-1177. DOI:10.1007/s00607-013-0369-2 |

| [13] |

Chen X,Xu C,Dick R P.Memory access aware on-line voltage control for performance and energy optimization[C]//Proceedings of the 2010 IEEE/ACM International Conference on Computer-Aided Design (ICCAD).San Jose:IEEE,2010:365-372.

|

| [14] |

Liu Xiaobin, Guo Bing, Shen Yan. Research on algorithmic power consumption BP network model of embedded software[J]. Journal of University of Electronic Science and Technology of China (Natural Science Edition), 2011, 40(6): 921-926. [刘啸滨, 郭兵, 沈艳. 嵌入式软件算法级功耗BP网络模型研究[J]. 电子科技大学学报(自然科学版), 2011, 40(6): 921-926.] |

| [15] |

Liu Xiaobin, Guo Bing, Shen Yan. Embedded software architecture-level energy consumption modeling method[J]. Journal of Software, 2012, 23(2): 230-239. [刘啸滨, 郭兵, 沈艳. 嵌入式软件体系结构级能耗建模方法[J]. 软件学报, 2012, 23(2): 230-239.] |

| [16] |

Mudge T.Vertigo:Automatic performance-setting for Linux[C]//Proceedings of the 5th Symposium on Operating Systems Design and Implementation.Berkeley:USENIX Association,2002:105-116.

|

| [17] |

Pallipadi V,Starikovskiy A.The ondemand governor:Past,present and future[C].Ottawa Linux Symposium,Ottawa,2006:657-672.

|

2018, Vol. 50

2018, Vol. 50